近期研究項目

靜電放電 (ESD)

靜電放電是系統級設計的重要課題之一。需要對組件和系統的 ESD 穩健性進行測試和審查,以允許在 ESD 保護區內進行安全處理和安裝。密蘇里科技 EMC 實驗室 ESD 項目的主題可以是片上 ESD 保護表徵、片外 ESD 保護設計或組合。

ESD 到集成電路 (IC)

靜電放電 (ESD) 事件可能導致集成電路 (IC) 的軟故障和硬故障。為了保護 IC 免受 ESD 的影響,ESD 保護結構對於芯片級設計至關重要。通常,IC 供應商已經設計了片上 ESD 保護。對於片外 ESD 保護設計人員,需要片上 ESD 保護模型以確定所需的片外 ESD 保護級別。

IO 最通用的 ESD 保護是帶有 VDD-VSS 電源箝位的雙二極管結構。由於 IC 端口連接的限制,需要利用三個端口,包括 VDD-VSS、IO-VSS 和 IO-VDD,才能使用傳輸線脈衝(TLP ) 測試。具有分離接地的電路板旨在將所有連接都包含在一個電路板上。該方法使用 VNA、TDR、TLP 和 VF-TLP 來表徵所有 ESD 保護二極管的小信號模型和大信號模型。

PCB板設計(左:頂視圖,右:中間層/GND層) 在一塊板上包含所有三個連接以進行 TLP 測試。

TLP 和 VF-TLP 設置圖

片上ESD保護結構圖

TLP系統設置

建模ESD保護器件

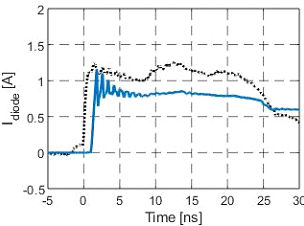

通常將瞬態電壓抑制 (TVS) 二極管等保護裝置添加到電路中,以提高其對靜電放電 (ESD) 的免疫力。確保 TVS 二極管在 ESD 事件期間導通,並且片上保護器件不承擔全部電荷可能具有挑戰性,但是,因為許多片上 ESD 保護結構將比關斷器件開啟更快且電壓更低芯片電視。這項工作開發了一種方法來預測系統對更複雜場景的響應——當 ESD 槍向連接到測試板的 USB 電纜的引腳放電時,該測試板包含受 TVS 二極管保護的 IC。該方法使用混合仿真技術,其中 ESD 槍、電纜和外殼之間的相互作用通過 3D 全波模型捕獲,TVS 和片上二極管的響應通過 SPICE 模型捕獲。工程師可以使用這種方法在更複雜的場景中評估和優化其 ESD 保護策略的有效性。

ESD 槍通過 USB 電纜接觸放電到 ESD 保護設備。

ESD 保護器件的 SEED 建模框架

TVS 電流。實測——虛��線;模擬 – 實線

片上二極管電流。實測——虛線;模擬 – 實線

片上二極管電壓。實測——虛線;模擬 – 實線